We understand that nursing assignments can be daunting and time-consuming for many students, which is why we have assembled a team of experienced nursing tutors who are ready to help you tackle any nursing capstone assignment or project.

Our tutors are highly qualified in the nursing field and have a deep understanding of the subject matter. They have hands-on experience in various nursing practices, which means they are equipped to handle any nursing-related assignments.

We take pride in our commitment to providing the best possible service to all nursing students. We believe that every student deserves a chance to succeed and our services are designed to give you just that.

Our services are tailored to meet the specific needs of each student. We understand that every student has unique requirements, and we work closely with you to create a customized solution that meets your needs.

With our nursing capstone assignment help, you can rest assured that your assignment will be completed to the highest standards. Our tutors follow a rigorous quality control process to ensure that all assignments are accurate, plagiarism-free, and delivered on time.

We are confident that our services will exceed your expectations, and we look forward to working with you. Don’t let nursing assignments hold you back anymore. Contact us today to learn more about our services and how we can help you succeed!

Our nursing tutors are experts in their field and have a deep understanding of nursing concepts. By working with our tutors, students can improve their understanding of the subject and achieve better grades.

We understand the importance of keeping our clients' personal information and assignments confidential. At our website, we take strict measures to ensure that all information is kept private and secure.

Our website provides nursing students with access to experienced tutors who are well-versed in the nursing field. This ensures that students receive accurate and detailed solutions to their nursing assignments.

We understand the importance of delivering quality work to our clients. That's why our team of nursing tutors follows a strict quality control process to ensure that all assignments are plagiarism-free, accurate, and of high quality.

Our nursing assignment help website features a team of highly qualified and experienced nursing tutors with a passion for helping nursing students succeed. Each of our tutors possesses a combination of academic qualifications, professional experience, and personal qualities that make them exceptional educators and mentors.

All our tutors are nursing professionals with advanced degrees in nursing, such as MSN or DNP. They have extensive experience within various healthcare settings, including hospitals, clinics, long-term care facilities, and educational institutions. This experience enables them to provide students with practical, real-world insights into the nursing field.

In addition to their academic achievements and professional experience, our nursing tutors possess excellent communication and interpersonal skills. They have the ability to communicate complex nursing concepts in a clear, understandable manner to students of all levels. They are patient, attentive, and make sure to tailor their tutoring style to the specific learning needs of each individual student.

Our nursing tutors are passionate about what they do and are committed to helping nursing students excel academically. They have a deep understanding of nursing concepts, theories, and principles, and they are committed to keeping up-to-date with the latest developments in the nursing field.

When working with our nursing tutors, students can expect personalized mentoring, support, and guidance to help them succeed in their nursing studies. From research and planning to writing and proofreading, our tutors have the expertise and experience necessary to provide high-quality tutoring services that will guarantee success.

In summary, our nursing tutors represent the very best in the nursing field, possessing the knowledge, experience, and passion needed to help nursing students succeed academically.

Pathophysiology Assignment Help

Understanding the complex mechanisms underlying diseases and disorders is vital for nursing students. If you’re struggling with pathophysiology assignments, our experienced tutors are here to provide top-notch Pathophysiology Assignment Help.

Pathophysiology delves into the study of abnormal physiological processes that occur in various diseases and conditions. Our tutors specialize in pathophysiology and can assist you in comprehending and completing assignments related to this subject. Whether it’s analyzing the pathogenesis of diseases, understanding the alterations in body systems caused by certain conditions, or discussing the manifestations and treatment options, our tutors have the expertise to guide you.

By availing our Pathophysiology Assignment Help, you will gain access to personalized guidance tailored to your assignment requirements. Our tutors will work closely with you to understand the objectives of your assignment, review your work, and provide valuable feedback to enhance its quality. With their in-depth knowledge in pathophysiology, they can help you excel in your assignments and develop a strong understanding of the underlying mechanisms of diseases and disorders.

Don’t let pathophysiology assignments overwhelm you. Invest in our Pathophysiology Assignment Help and unlock your potential as a nursing student. Our tutors are dedicated to your success and are here to provide you with accurate information, evidence-based strategies, and unwavering support in your nursing journey. Trust us to be your dependable resource for all your pathophysiology assignment needs.

Pneumonia Assignment Help

Pneumonia is a common respiratory infection that affects the lungs and can cause severe illness, especially in vulnerable populations. As a nursing student, understanding the etiology, risk factors, manifestations, and management of pneumonia is crucial.

Our tutors specialize in pneumonia nursing and can assist you in understanding and completing assignments related to this subject. Whether it’s discussing the different types of pneumonia, analyzing diagnostic tests, or developing nursing care plans for patients with pneumonia, our tutors have the expertise to guide you.

By availing our Pneumonia Assignment Help, you will gain access to personalized assistance tailored to your assignment requirements. Our tutors will work closely with you to understand the objectives of your assignment, review your work, and provide valuable feedback to enhance its quality. With their extensive knowledge in pneumonia nursing, they can help you excel in your assignments and deepen your understanding of this critical respiratory infection.

Don’t let pneumonia assignments overwhelm you. Invest in our Pneumonia Assignment Help and unlock your potential as a nursing student. Our tutors are dedicated to your success and are here to provide you with accurate information, evidence-based strategies, and unwavering support in your nursing journey. Trust us to be your dependable resource for all your pneumonia nursing assignment needs.

Cardiac Nursing Assignment Help

Cardiac nursing focuses on the care and management of patients with heart-related conditions, emphasizing prevention, treatment, and rehabilitation. As a nursing student, understanding the anatomy and physiology of the cardiovascular system, common cardiac diseases, and specialized cardiac interventions is essential.

Our tutors specialize in cardiac nursing and can assist you in understanding and completing assignments related to this subject. Whether it’s analyzing ECG readings, developing care plans for patients with heart failure, or discussing cardiac medications and interventions, our tutors have the expertise to guide you.

By availing our Cardiac Nursing Assignment Help, you will gain access to personalized assistance tailored to your assignment requirements. Our tutors will work closely with you to understand the objectives of your assignment, review your work, and provide valuable feedback to enhance its quality. With their extensive knowledge in cardiac nursing, they can help you excel in your assignments and deepen your understanding of this critical nursing specialty.

Don’t let cardiac nursing assignments cause you stress and confusion. Invest in our Cardiac Nursing Assignment Help and unlock your potential as a nursing student. Our tutors are committed to your success and are here to provide you with accurate information, evidence-based strategies, and professional guidance. Trust us to be your dependable resource for all your cardiac nursing assignment needs.

Pediatrics Nursing Assignment Help

Pediatrics nursing focuses on caring for infants, children, and adolescents, addressing their unique healthcare needs. As a nursing student, understanding the growth and development of children, common pediatric conditions, and specialized interventions is essential.

Our tutors specialize in pediatrics nursing and can assist you in understanding and completing assignments related to this subject. Whether it’s discussing childhood vaccination schedules, analyzing pediatric care plans, or exploring family-centered care approaches, our tutors have the expertise to guide you.

By availing our Pediatrics Nursing Assignment Help, you will receive personalized assistance tailored to your assignment requirements. Our tutors will work closely with you to understand the objectives of your assignment, review your work, and provide valuable feedback to enhance its quality. With their in-depth knowledge in pediatrics nursing, they can help you excel in your assignments and develop a solid understanding of this critical nursing specialty.

Don’t let pediatrics nursing assignments stress you out. Invest in our Pediatrics Nursing Assignment Help and gain the knowledge and confidence to excel in your nursing studies. Our tutors are passionate about your success and are here to provide you with accurate information, evidence-based strategies, and unwavering support in your journey to becoming a pediatric nurse. Trust us to be your reliable partner in achieving excellence in pediatrics nursing.

Aged Care Nursing Assignment Help

Aged care nursing focuses on providing comprehensive and specialized care for older adults, addressing their unique physical, emotional, and social needs. As a nursing student, understanding the aging process, common age-related conditions, and gerontological nursing interventions is essential.

Our tutors specialize in aged care nursing and can assist you in understanding and completing assignments related to this subject. Whether it’s discussing the management of chronic diseases in older adults, analyzing age-related changes in the body, or exploring ethical considerations in geriatric care, our tutors have the expertise to guide you.

By availing our Aged Care Nursing Assignment Help, you will receive personalized assistance tailored to your assignment requirements. Our tutors will work closely with you to understand the objectives of your assignment, review your work, and provide valuable feedback to enhance its quality. With their in-depth knowledge in aged care nursing, they can help you excel in your assignments and develop a solid understanding of this critical nursing specialty.

Don’t let aged care nursing assignments cause you stress and confusion. Invest in our Aged Care Nursing Assignment Help and gain the knowledge and confidence to provide exceptional care to older adults. Our tutors are committed to your success and are here to provide you with accurate information, evidence-based strategies, and professional guidance. Trust us to be your dependable resource for all your aged care nursing assignment needs.

Mental Health Nursing Assignment Help

Mental health nursing focuses on promoting mental well-being, preventing mental disorders, and providing care for individuals with psychiatric conditions. As a nursing student, understanding the principles of mental health, therapeutic communication techniques, and evidence-based interventions is crucial.

Our tutors specialize in mental health nursing and can assist you in understanding and completing assignments related to this subject. Whether it’s discussing therapeutic approaches, analyzing mental health assessment tools, or developing care plans for patients with psychiatric disorders, our tutors have the expertise to guide you.

By availing our Mental Health Nursing Assignment Help, you will receive personalized assistance tailored to your assignment requirements. Our tutors will work closely with you to understand the objectives of your assignment, review your work, and provide valuable feedback to enhance its quality. With their in-depth knowledge in mental health nursing, they can help you excel in your assignments and develop a solid understanding of this critical nursing specialty.

Don’t let mental health nursing assignments cause you stress and confusion. Invest in our Mental Health Nursing Assignment Help and gain the necessary knowledge and skills to provide compassionate care for individuals with psychiatric conditions. Our tutors are committed to your success and are here to provide you with accurate information, evidence-based strategies, and professional guidance. Trust us to be your dependable resource for all your mental health nursing assignment needs.

Palliative Care Nursing Assignment Help

Palliative care nursing focuses on providing compassionate care to individuals with serious illnesses, focusing on the relief of pain, management of symptoms, and enhancing quality of life. As a nursing student, understanding the principles, ethical considerations, and interventions in palliative care is crucial.

Our tutors specialize in palliative care nursing and can assist you in understanding and completing assignments related to this subject. Whether it’s discussing communication strategies with terminally ill patients, analyzing pain management approaches, or exploring the psychological and spiritual aspects of care, our tutors have the expertise to guide you.

By availing our Palliative Care Nursing Assignment Help, you will receive personalized guidance tailored to your assignment requirements. Our tutors will work closely with you to understand the objectives of your assignment, review your work, and provide valuable feedback to enhance its quality. With their extensive knowledge in palliative care nursing, they can help you excel in your assignments and develop a solid understanding of this crucial nursing specialty.

Don’t let palliative care nursing assignments overwhelm you. Invest in our Palliative Care Nursing Assignment Help and unlock your potential as a nursing student. Our tutors are committed to your success and are here to provide you with accurate information, evidence-based strategies, and professional guidance. Trust us to be your dependable resource for all your palliative care nursing assignment needs.

Anatomy Nursing Assignment Help

Anatomy is the study of the structure and organization of the human body, which is crucial for understanding the functions and relationships of different body systems. As a nursing student, having a solid foundation in anatomy is essential for clinical practice and patient care.

Our tutors specialize in anatomy nursing and can assist you in understanding and completing assignments related to this subject. Whether it’s identifying anatomical structures, analyzing the relationship between anatomy and physiology, or applying anatomical knowledge in nursing assessments and interventions, our tutors have the expertise to guide you.

By availing our Anatomy Nursing Assignment Help, you will receive personalized guidance tailored to your specific assignment requirements. Our tutors will work closely with you to understand the objectives of your assignment, review your work, and provide valuable feedback to enhance its quality. With their in-depth knowledge in anatomy nursing, they can help you excel in your assignments and develop a strong understanding of the human body’s intricacies.

Don’t let anatomy nursing assignments overwhelm you. Invest in our Anatomy Nursing Assignment Help and unlock your potential as a nursing student. Our tutors are dedicated to your success and are here to provide you with accurate information, evidence-based strategies, and unwavering support in your journey to becoming a knowledgeable healthcare professional. Trust us to be your reliable partner in mastering anatomy in the nursing field.

Neurosurgery Nursing Assignment Help

Neurosurgery nursing involves the care and management of patients undergoing surgical procedures on the brain, spinal cord, and peripheral nerves. As a nursing student, understanding the intricate details of neurosurgical procedures, pre- and post-operative care, and potential complications is crucial.

Our tutors specialize in neurosurgery nursing and can assist you in understanding and completing assignments related to this subject. Whether it’s discussing neurosurgical interventions, analyzing imaging tests, or developing nursing care plans for patients with neurological conditions, our tutors have the expertise to guide you.

By availing our Neurosurgery Nursing Assignment Help, you will receive personalized guidance tailored to your assignment requirements. Our tutors will work closely with you to understand the objectives of your assignment, review your work, and provide valuable feedback to enhance its quality. With their extensive knowledge in neurosurgery nursing, they can help you excel in your assignments and develop a solid understanding of this specialized area.

Don’t let neurosurgery nursing assignments overwhelm you. Invest in our Neurosurgery Nursing Assignment Help and unlock your potential as a nursing student. Our tutors are dedicated to your success and are here to provide you with accurate information, evidence-based strategies, and unwavering support in your journey to becoming a skilled neurosurgery nurse. Trust us to be your reliable resource for all your neurosurgery nursing assignment needs.

Double / Single spacing

APA/MLA and more

300 / 600 words per page

Bibliography page

One-inch margins

Times New Roman, 12 pt

Bibliography

Cover (Title) Page

Simple Outline

Plagiarism Report

Unlimited revisions

Support 24/7

It is a service that provides support and guidance to nursing students in completing their capstone coursework assignments, essays, research papers, dissertations, and other nursing-related assignments. It involves working with experienced nursing tutors who provide personalized assistance and help students succeed in their nursing studies.

Nursing assignment help services can benefit nursing students at all levels of their academic careers, whether they are just starting out or already enrolled in advanced courses. Nursing students who need help with challenging coursework assignments, research papers, essays, or dissertations can benefit the most from nursing assignment help services.

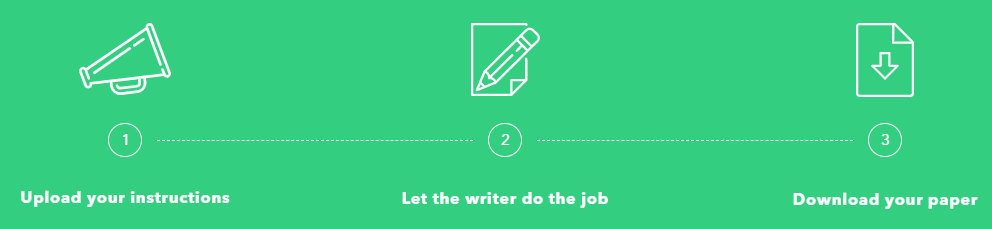

To get started with nursing assignment help services, simply visit our website and select the service that best fits your needs. You can then submit your nursing assignment, and our experienced nursing tutors will provide you with the necessary guidance and support to complete it successfully. You may be asked to create an account or provide information on your assignment and academic background, depending on the service you choose.

Yes, all our nursing tutors have advanced degrees in nursing, such as MSN or DNP, and have extensive experience working in various healthcare settings. They possess the knowledge, expertise, and experience necessary to provide high-quality nursing assignment help services to nursing students.

Yes, we take confidentiality very seriously and ensure that every student’s personal information and assignments remain secure and private. We do not share any information with third-parties and have strict data privacy policies to ensure that our clients’ data is protected.

The cost of nursing assignment help services varies depending on the specific service you require and the complexity of your assignment. Our pricing is competitive and affordable, and we offer a range of payment options to accommodate the needs of nursing students. We strive to provide accessible nursing assignment help services to students without breaking the bank.

Yes, we guarantee that all nursing assignments delivered to our clients will be 100% plagiarism-free. Our nursing tutors conduct extensive research and ensure that all work is original and free from any form of plagiarism. We take academic integrity very seriously and ensure that our clients receive original work that meets the necessary academic standards.

In the unlikely event that a student is not satisfied with our services, we offer revision services to address any concerns or issues. We work with our clients to ensure that they receive the necessary help and support throughout their nursing studies and achieve academic success.

Our nursing assignment help services provide a range of benefits to nursing students , including 24/7 customer support, expert nursing tutors, quality assurance, strict confidentiality measures, personalized assistance, and quick turnaround times. We take pride in providing high-quality nursing assignment help services that are tailored to meet the specific needs and requirements of each individual student.

2023 Academic Homework Market. Online writing and editing services.